近日,中国移动研究院数字中频核心算法成功在极芯通讯UC1040芯片上完成性能测试。该算法用于小基站场景下功率放大器的非线性失真矫正,以提升功率放大器效率。本次测试成功,一方面将加速国产芯片的进程,降低核心算法的技术门槛,推动5G小基站产品生态多样化发展;另一方面将补充国产芯片缺乏中频核心算法的短板,完善国产芯片产业能力,标志着5G国产化高性能芯片的产品化落地。

数字中频核心算法技术是目前应用最广泛的功放线性化技术,通过增加反馈链路对功率放大器的非线性失真和记忆特性进行自适应学习,得到功率放大器的非线性失真特性参数;再利用预失真器将发射信号预先进行逆非线性特性失真,使其经过功率放大器时与其非线性特性进行抵消,从而解决功率放大器在高效率区工作时固有的带外发射干扰和带内失真问题,间接提升功率放大器的效率。

在小基站设备中,提高功放效率的传统方式主要有两种:一方面是通过功率回退的方式来避免功放工作在非线性区,另一方面是利用国外现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)或无线电收发两用(Transceiver)芯片厂家提供的高性能数字中频核心算法 IP来实现。面对新兴国产芯片目前缺乏数字预失真算法的问题,中国移动研究院自主研发数字中频核心算法方案,提升自主可控度,算法具备低资源消耗、高性能矫正、大幅提升效率的优势,并可通过灵活配置模型架构适适应国内外砷化镓(GaAs)、横向扩散金属氧化物半导体(LDMOS)、氮化镓(GaN)等多种功率放大器,满足5G小基站不同场景需求。

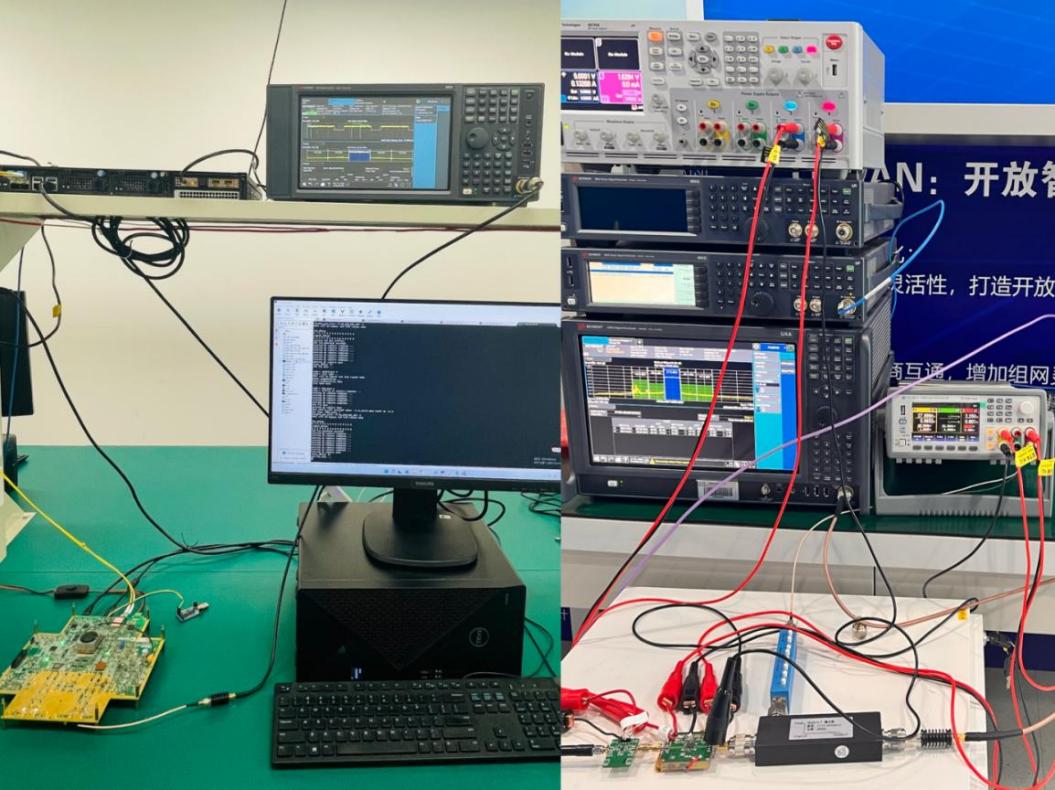

测试环境

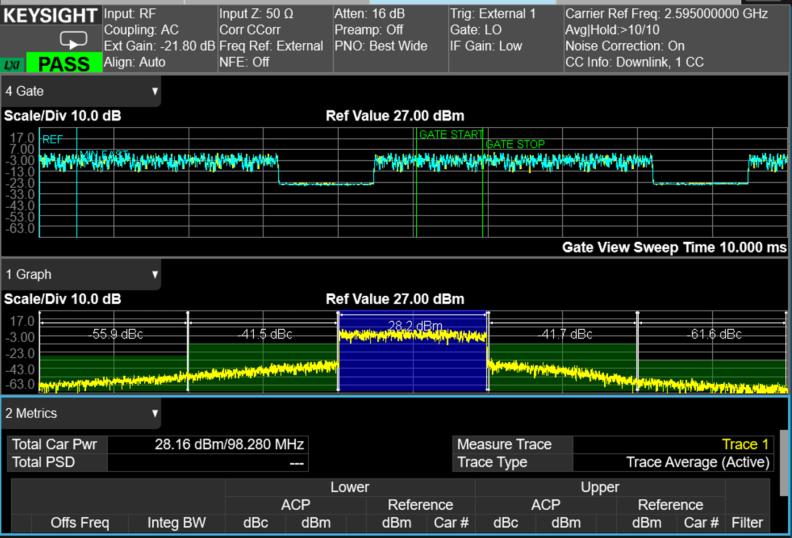

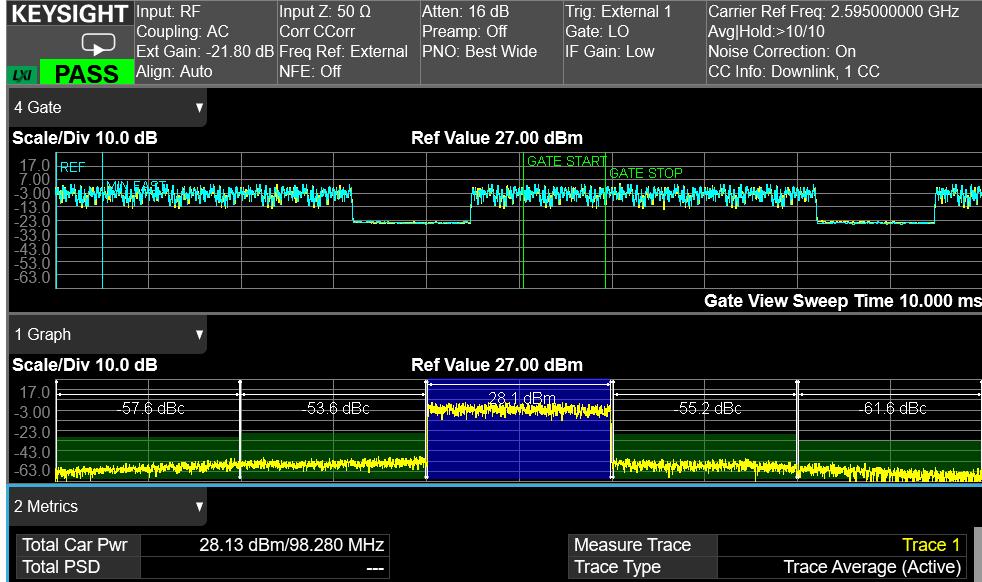

中国移动研究院自主研发的数字中频核心算法充分利用UC1040芯片硬件资源,针对于LDMOS、GaN、AsGa等多种功率放大器的数字中频核心算法模型选取和参数配置进行了筛选和优化,均达到良好的校准效果。在没有功率回退的情况下,邻道功率泄露比(ACPR)达到-53dBc的优异性能;相对于开环控制,闭环控制性能达到-13dBc。

功率放大器额定输出功率时非线性前后ACPR结果

UC1040芯片是极芯通讯在2021年6月推出的全球第一颗真正支持O-RAN标准的5G基站数字前端(DFE)芯片。该芯片集成了四个收发通道,支持Option8和Option7-x的RAN功能划分接口,支持波峰因子消除(CFR)和可编程数字预失真(DPD)能力。目前已完成5G上下行流量测试,多家厂商基于UC1040芯片开发了多款RRU产品。