�����ؼ��ʣ�ͨ�ŵ�̨��ͨ��Э�飻DSP��FPGA

һ������

�����κ�ͨ��ϵͳ����һ����ͨ��Э��֧�������ͨ�ŵ�����һ��ͨ��ϵͳ���ٰ���������ͨ��Э�����·��ͨ��Э�顣������ͨ��Э��������������·��ʵ��֮��Ϊλ��������Ҫ���������ӵĽ��������ֺͲ���ṩ�����ġ���е�ġ������Ե����ԡ���·��Э������ͨ��ϵͳ�����������������Ļ����Ͻ�һ�������Ϳ��ƣ���Ҫ��ɽ�����·�������·���������ơ�ͬ�����ƺͲ�����ƵĹ��ܡ����������ͨ��Э����Ҫ����������Э�����·��Э�飬����ͨ�ŵ�̨������֤������һ�ֿɿ��ĸ�Ч��ͨ��Э�飬���нϸߵ������������Ӧ�ü�ֵ��

����ͨ��Э���ԭ��

�������������һ��ͨ��Э������һ������ͨ�ŵ�̨�ϣ���Э���ܺܺõ������ͨ�ŵ�̨��Ъʽ������Ҫ����ԭ����ͼ1��ʾ��

����������ͨ�ŵ�̨�����߽��յ���Ϣʱ���ϱ�Ƶģ�����Ƶ�˵��������ֳ��ɱ��������������FPGA�����н��룬FPGA���������ݷ���FPGA�ķ������ݻ��������˻�������С����Ϊ1024 byte��С�����˻�������ʱ����һ�ж��źŴ��������źŴ�������DSP����DSP�ڿ���һ����СΪ1 024 byte�Ļ�����txqueue��txqueueͨ���������߷�ʽ����FPGA���������ݣ���txqueue��ʱ����ͨ��DSP�Ķ�ʱ���жϷ�ʽ��txqueue�ڵ�1 024 byte�����ݷ����ӿ�������MAX3111E���ڵķ�������Buffer����Buffer�ڵ��������շ������˼����(PC)��PC������Щ���ݽ��з����ʹ�����

������PC�������ݺ�����Ҫ����ʱ�����Ȱ�PC�ڵ����ݻ�������9 600 bps���ٶ�ͨ��MAX3111E�Ľ�������FIFO���͵�DSP��1 024 byte��С�����ݻ�����rxqueue����rxqueue��������ʱ����ѯFPGA�Ľ������ݻ�����û�пգ����FPGA�Ľ��ջ�������ʱ�����rxqueue�����ݷ���FPGA�Ľ������ݻ�������FPGA�Խ��ջ����������ݽ��б��봦�������ϱ�Ƶģ�顣PC�����͵�֡��������֡������֡��֡�ṹ���1�ͱ�2��ʾ��

��������֡������DSP���Ϳ������ػ�����λ������������ص�̨�Ĺ���������֡���ڶ���PC��DSP�������ݽ����ĸ�ʽ������֡��5 byte����5��8 bit���� �� ֡ ͷΪ70 H��70 H��ʾһ֡��ʼ���䣬data1��ʾ��Ҫ���͵���������������ػ�����λ�ȣ���У�������ڼ������������Ƿ���ȷ��֡β7EH��ʾ֡�������������֡��128 byte����128��8 bit������֡ͷΪ7EH��7EH��ʾһ֡��ʼ���䣬Point1��Point0���ڼ����Ѵ����֡�ĸ�����Point1��ʾ�������ĸ�λ��ֵ��Point0��ʾ�������ĵ�λ��ֵ��data0��data121��ʾ��Ҫ���͵����ݣ�У����CRC1��CRC0���ڼ������������Ƿ���ȷ������֡����ѭ��У����CRC��16λУ�鷽ʽ����֡���������־��У���������ʾ����֡�����������

����ͨ��Э���ʵ��

1.ͨ��Э���Ӳ��ʵ��

����ͨ��Э���Ӳ��ʵ������ͨ�ŵ�̨�����źŴ�����Ӳ��ƽ̨��ʵ�ֵģ�ͨ��Э���������Ӳ��ʵ�ֵĹؼ�����DSP��PC�������ݵ�·��FPGA��DSP�������ݵ�·�����֡�DSP��PC����������ͼ2��ʾ������TMS320VC5416��DSPΪͨ�ŵ�̨�Ļ�������оƬ��DSPͨ��MAX3111E��UART�ӿ�оƬ��PC���������ݣ�MAX3111EоƬ���з������ݻ������ͽ������ݻ���������MAX3111E�յ�DSP������һ��byteʱ����յ�PC������һ��byteʱ�������жϴ����źŴ���DSP���ⲿ�ж�����INT3����DSP������ݵ��շ����Ӷ��ﵽ��PC�������ݵ�Ŀ�ġ�FPGA��DSP����������ͼ3��ʾ��FPGA���ͻ�����������ջ�������ʱ������һ�͵�ƽ����DSP��һ���ⲿ�жϣ���INT2�����������жϷ���������ж���FPGA���ͻ��������¼��������жϻ���FPGA���ջ��������¼��������жϣ������FPGA���ͻ��������¼��ж�ʱ��FPGAͨ���������߷�ʽ��DSP�������ݣ������FPGA���ջ��������¼��ж�ʱ��DSPͨ��MCBSP1�ڷ���������FPGA�Ľ��ջ�������FPGA���ݻ���ջ���״̬��ΪDSP���жϴ����¼���������DSP��CPU���ò�ѯ��ʽ����ʡ��DSP��CPU��Դ������������

2. ͨ��Э�������ʵ��

����ͨ��Э�������ʵ�ֳ������̰�����̨�������ݺ͵�̨�������������֣���̨�շ����ݵij���������ͼ1����ʾ��ͨ��ԭ��������ͬ��������C5416��DSPΪ�����źŵ����������������±�Ƶģ�����������ź���ɽ�����ͬ���ȹ��ܺ����ȥ�����ż���ŵ��㷨������FPGA��ɱ����źŵĽ��룬�������ź���C5416ͨ��MAX3111E�ӿڵ�·�ϴ���PC����PC������Ҫ��������ݻ�����ͨ��MAX3111E��C5416��FPGA�����źű��������ŵ����ŵ����á�������Ӳ��ƽ̨�ϲ���TPC��64��57��x��32��26�����ŵ����뷽ʽ�����ҽ�������ƥ�䣨����Ϊ0.75����1.6 s��֯���ڸ�˹�ŵ��¿��Ի�ô�Լ2.5dB�����棬��������ͼ4��ʾ���������ŵ��¿��Ի�ô�Լ4 dB�����棬��������ͼ5��ʾ��

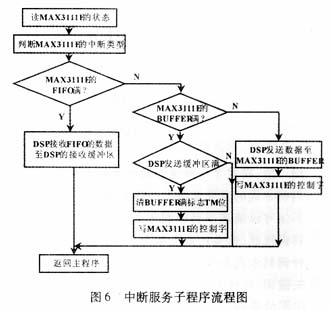

������ͨ��Э�������ʵ�ֵ��ѵ����������MAX3111E�ӿ�оƬʵ��DSP��PC�����ݽ�����Ӳ���ӿ���ͼ2��ʾ������DSPͨ����ͨ������ڣ�MCBSP�������ڴ���ͬ���ӿڣ�SPI��Э�鷽ʽ��������Ҫ����MCBSP�ij�ʼ������MAX3111E����������DSP�ⲿ�ж�INT3�ķ����ӳ���Ȳ��֣������ж�INT3�ķ����ӳ�������ͼ��ͼ6��ʾ��

�ġ�����

����ͨ��ͨ�ŵ�̨�IJ��Խ����������ͨ��Э�������ȷ���ɿ�����˳���ر���ͨ�ŵ�̨֮����Ϣ���շ������нϸߵ�����ָ�������ʵ�ʹ���Ӧ�ü�ֵ��

�����

��1�ݳ�����������������Ƽ.һ������ͨ�ſ�������ʵ�֣ۣʣ�.������ͨ��ѧѧ����2002����7��.

��2�������������ģ��ƽ�������.һ�ֻ����������ߵ���źŴ��������ۣʣ�.ͨ��ѧ��.

��3��TMS320VC5416 DSP Reference Set�ۣڣ�.TI��˾.

��4��MAX3111E Reference Manual�ۣڣ�.Maxim ��˾.

��5�ݴ����壬�ܽ���.TMS320C54x DSP�ṹ��ԭ����Ӧ�ãۣͣ�.�������������պ�������磬2001.

��6�ݺ����裬��ʢ�������źŴ���ϵͳ��Ӧ�ú���ƣۣͣ�.�Ϻ����Ϻ���ͨ��ѧ�����磬2003.

���ר�⣺

���ר�⣺