本文讨论了高速串行链路中常用的测试码型伪随机码流的原理,以及不同的测试码型对物理层测试结果的影响。

高速串行总线的常用测试码型

在当今的电信和计算机产品上,相比传统的并行总线,电路中的串行总线越来越多,速率越来越快。比如通信产品中的10GBase-KR、CPRI2代,计算机中的PCIeGen2、SATA6G,存储产品中的SAS6G、FC8.5G,这些串行总线都陆续的跨过了5Gbps。由于速率比较高,使得串行总线上的相关的收发器芯片(SERDES)、连接器、单板、背板的设计面临着越来越多的挑战。对于这些高速串行总线的物理层测试,测试码型的选用至关重要,在很多串行总线的规范中对测试码型有严格的要求。本文将对此进行探讨。

首先,串行总线的物理层测试通常分为发射机测试和接收机测试,又称为TX测试和RX测试。发射机测试通常包括眼图、抖动、信号波形、幅度、上升下降时间等测试项目,接收机测试通常包括误码率、抖动容限、接收机灵敏度等测试项目。对于眼图测试、误码率和抖动容限测试,最常用的测试码是伪随机码(PseudoRandomBinarySequence,简称PRBS),主要有PRBS7、PRBS15、PRBS23和PRBS31。除了PRBS以外,K28.5、1010、CJPAT等码型在很多串行总线的物理层测试中都很常用,特别是计算机上的串行标准(比如SATA、USB3.0、SAS)的测试码型有所不同,在本文中主要讨论最常用的测试码型——PRBS。

PRBS的实现方法

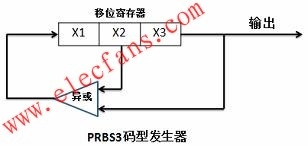

顾名思义,PRBS是伪随机码流,在其码流中包括了所有可能出现的比特组合,而且其出现的概率是相同的。PRBS信号是由PRBS码型发生器生成的。PRBS发生器通常是由线性反馈移位寄存器(LinearFeedbackShiftRegister,简称LFSR)和异或电路组成。如下图1所示为最简单的PRBS3的码型发生器,其多项式为X3+X2+1,即寄存器的第3位与第2位做异或(XOR)的逻辑运算后返回到寄存器的第1位,寄存器的第3位X3同时也是PRBS3发生器的输出。

图 1:PRBS3码型发生器原理

在表格1中显示了PRBS3的n个周期的时钟后输出n个比特的码流。X1/X2/X3分别是3个比特移位寄存器的低位到高位,输出位是X3,初始状态为X1/X2/X3=1/1/1,如表格第1行所示。

第1个时钟沿到达后,X3与X2异或后等于0,输入到X1,同时X1和X2前移到X2和X3,所以X1/X2/X3=0/1/1,如表格第2行所示;

第2个时钟沿到达后,X3与X2异或后等于0,输入到X1,同时X1和X2前移到X2和X3,所以X1/X2/X3=0/0/1,如表格第3行所示;

第3个时钟沿到达后,X3与X2异或后等于1,输入到X1,同时X1和X2前移到X2和X3,所以X1/X2/X3=1/0/0,如表格第4行所示;

……

以此类推,第5行为0/1/0,第6行为1/0/1,第7行为1/1/0,第8行为1/1/1,与初始状态相同,接下来的第9行和第10行与第2行和第3行完全相同,也就是说PRBS3的码型输出7个比特后开始重复。X3是PRBS3的输出位,所以PRBS3输出的码型为1110010,码长为7,如图2所示,每7个比特后开始重复输出同一码型。在PRBS3中包括了11100属于码流中频率最低的码型,010是频率最高的码型。

表格1:PRBS3的3位寄存器数值

图2:PRBS3输出信号

为何PRBSN的码长为2^N-1

在PRBS3的3位寄存器可以产生2的3次方合计8个排列组合。采用XOR异或电路的PRBS发生器在3个比特都是0的时候,下一个时钟到来的时候,第3个比特和第2个比特异或后还是0,输入到寄存器的第一位还是0,同时第1个和第2个比特前移到第2个和第3个比特,这样,移位后寄存器的3个比特都是0,则PRBS发生器的输出一直都是0,被锁住。所以PRBS3码流中不能出现3个全0的比特,这样,PRBS3的组合方式为2^3-1=7共7种,码长位7个比特。同理,PRBS7的码长为2^7-1=127个比特,PRBS15的码长为2^15-1=32767个比特。

PRBS7和PRBS31

PRBS7是目前10Gbps以下的串行总线中最常用的测试码型。常用的PRBS7的多项式为X7+X6+1,码长为127个比特,在ITU-TV.29规范中规定。PRBS7属于短伪随机码型,与8b10bNRZ编码的数据流很相似,所以,在PCIe、SATA、XAUI、1000BASE-LX、FC、SAS等采用8b10b编码的串行总线中,PRBS7是最常用的测试码型,支持这些总线的芯片通常都可以输出PRBS7测试码型,用于眼图、抖动或误码率测量。

图 3:PRBS7码型发生器原理

PRBS7的码流中最长的连1为7个,最长的连0为6个;而8b10b编码中最长的连1为5,最长的连0也是5;因此,相比8b10b编码,PRBS7可以产生的较低频率的码型。使用PRBS7作为驱动源,在同一信道(比如背板上20英寸长走线)上传输到接收端后得到眼图和抖动,都比8b10b编码的作为驱动源时的结果稍差些。这样,PRBS7作为8b10b编码的串行总线的测试码型,留出了一定的设计余量。

图4:几种常用PRBS的说明

PRBS31的多项式为X31+X28+1,码长为2^31-1=2147,483,647个比特,属于长伪随机码型。码流中最长的连1为31个,最长的连0为30个,包含了相当多的低频成分而这正是SONET/SDH系统测试规范中所要求的,所以可用于像SONET/SDH信号那样包含了很多低频成分的物理层测量。

除了PRBS外,K28.5也是常用的测试码型之一。K28.5是8b10b编码表中的一个命令字,也是采用8b10b编码的串行链路中最常用的测试码型,由K28.5-=0011111010和K28.5+=1100000101组成,它有五个连续的1和五个连续的0,是8b10b编码中最长的连1和连0,也就是说K28.5包括了8b10b编码中最低频的码型,同时,K28.5中有101和010这样的高频码型,因此,K28.5非常适合测量和SI仿真时作为驱动端的激励,来计算信道的码间干扰(又称ISI)。我们知道,在8Gbps以下的串行总线上,8b10b编码是最常用的编码技术,这样也导致了K28.5是最流行的测试码型之一。在FC和XAUI标准中,也规定了K28.5为固有抖动的测试码型。

各种测试码型在同一信道上传输到接收端的测试结果分析

图5所示为高速背板、电缆的物理层测试的示意图,在发送端使用码型发射器作为驱动信号源,接收端使用误码检测器测量误码,或者使用示波器测量眼图。这样,就组成了完整的高速背板、电缆的物理层测试系统。

图5:高速印刷电路板的评估与测试系统

在本次测试中,我们使用了美国Centellax公司的可编程码型发生器PPG12500,PPG12500的输出信号速率可在1G到12.5Gbps任意调节。把输出信号的比特率设置为10.3125Gbps,幅度1V,去加重为1dB,输出码型分别为PRBS7/15/23/31。信道为某24英寸长PCB走线,在接收端使用Centellax的误码仪PCB12500测量误码率。表格2为测试结果,可见,驱动码型为短码型PRBS7时,误码率为0,而驱动码型为长码型PRBS31时,接收端的误码率最高。随着串行速率不断升高,8b10b编码在某些高速率链路上已不被采用,因此,在这些链路中很少使用PRBS7作为测试码型,几乎都使用了PRBS31作为测试码型,以产生最大的抖动和最恶化的激励信号。

表格2:误码率测试结果

Centellax的PPG12500产品介绍,特点,应用范围。

Centellax公司的PPG12500是速率在1-12.5Gbps可调的可编程码型发射器,相比其他码型发射器,有以下特点:

1.可编程码型长度高达24M个比特

2.内置了2个tap的去加重,可以用于评估某特定长度背板走线的TX端所需的去加重程度,而很多码型发射器都没有内置去加重功能,必须使用昂贵的外置去加重仪器附件。如下图6所示为示波器测量PPG12500输出的某6dB去加重的波形。

3.抖动透明传递功能,即码型发射器的参考输入时钟中注入抖动后,PPG12500的输出数据中也带有同类型抖动。如下图7为PPG12500搭配Centellax的时钟源TG1C1A,可以输出比特率为1-12.5Gbps、带有正弦抖动的串行数据。

4.可前面板控制,或者使用USB和GPIB遥控,提供了Labview驱动或者GUI来控制。

图6:PPG12500输出的带6dB去加重的码型

图7:Centellax的码型发射器PPG12500与时钟源TG1C1A

结语

在高速数字电路的互联设计中,伪随机码型PRBS是最常用的测试码型,Centellax的解决方案(码型发射器PPG12500加时钟源TG1C1A)提供了1-12.5G的比特率任意可调、集成去加重、可注入正弦抖动等强大功能,可以作为验证高速背板与高速电缆的驱动信号源、或者接收机抖动容限的加压信号源、以及发送端去加重程度的仿真器,是目前业界最高性价比的码型发生器。

作者:张昌骏 来源:美国Centellax公司

相关专题:

相关专题: