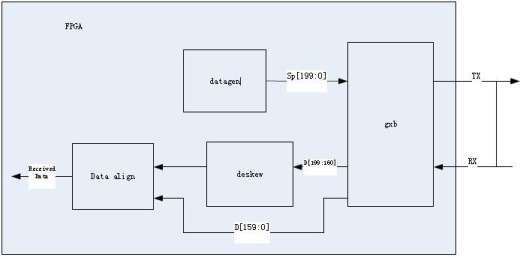

SFI-S(scalable SERDES framer interface)是40G/100G 光接口的高速串行通讯协议。这个协议采用单通道速率在10Gbps 左右的多个数据通道和纠偏通道。数据通道的数目在4 到20 之间。本文讨论了在ALTERA 的STRATIX4 GT 器件上实现40G SFI-S 协议。实现架构设计可分为发送与接收两部分,其总体框图如下图所示。

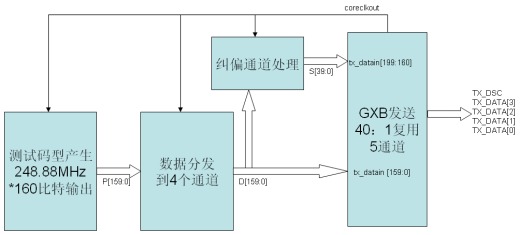

发送通道的架构如下图所示

根据STM-256 (39.8Gbps)帧结构,每帧622080(9x270x256 )字节,以768个A1(0xF6)和768个A2(0x28)开始。考虑到逻辑实现至少需要160位接口位宽(此时时钟运行在248.832MHz),测试数据产生结构如下。

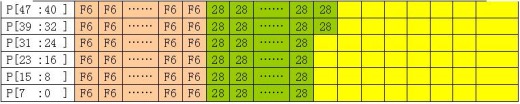

下图第一行为时钟节拍数,第一列为160位数据总线的数据码型(Pattern)黄色填充部分可直接用递增计数器。总共31104拍完成一帧,然后重复发送。

数据分发模块

D[159:0]是最终送到GXB的,GXB例化5通道,发送侧对逻辑接口为tx_datain[199:0]。其中tx_datain[199:140]连接纠偏通道输出的S[39:0]。 tx_datain[159:0]连接到数据分发模块的D[159:0]。

D[159:0]和P[159:0]之间的对应关系如下:

for i = 0 to 159, i++

If ( MOD(i,10) > 4) //MOD(i,j)指i被j除后的余数, 如MOD(159,10)=9

D[i] = P[ ( MOD(i,40)*4 + (i - MOD(i,40))/40 ) ]

else

D[i] = !P[ ( MOD(i,40)*4 + (i - MOD(i,40))/40 ) ] //!表示取反比特D[159:120]最终会通过SERDES通道3发送,比特D[119:80]最终会通过SERDES通道2发送,比特D[79:40]最终会通过SERDES通道2发送,比特D[39:0]最终会通过SERDES通道0发送。

纠偏通道处理模块

首先产生纠偏通道(deSkew)的40位数据S[39:0],最终D[199:160] = S[39:0]。

S[i]的产生需要组合逻辑,比如S[0]就是当前时钟拍的S[4:1]的奇校验结果。

作者:Altera 韦俊伟 蔡海宁 来源:电子工程专辑