0 引言

现阶段用于数字图像处理的系统有很多种,而从成本、性能、开发难易程度等多方面的考虑,基于FPGA和DSP的灵活性高、实用性强、可靠性高的图像压缩系统脱颖而出。在该种结构的图像处理系统当中,FPGA和DSP之间数据的通信方式和速度,将直接影响着整个图像处理系统的效率。

本文试图借助于ALTERA公司的低功耗FPGA(EP1C12Q240)、TI公司的DSP(TMS320VC5502)和一片CYPRESS公司双口RAM(CY7C025),设计出一种功耗低、设计灵活、能够实现复杂处理算法且高效、稳定的图像处理系统。

1 系统总体设计

系统主要模块分为电源管理模块、图像采集模块、速度采集模块、主控源模块及辅助控制模块。整个高速图像处理系统主要由CMOS图像传感器(MT9M011)、FPGA(EP1C12Q240C8)、双口RAM(CY7C025)、DSP(TM320VC5502)、视频D/A(ADV7123)和一些存储器等组成,如图1所示。首先,在图像采集模块控制COMS图像传感器下,图像数据则以25 f/s的速率向FPGA输送。然后,通过FPGA的控制使其缓存在片外的SDRAM中,之后实时显示模块控制ADV7123做到了对图像的实时显示。如果用户通过外部控制,选择了压缩模式,则原始的图像数据将由帧存模块移至高速缓冲模块中,DSP通过EMIF接口外扩存储器的方式,高效的读取双口RAM中的图像数据。最后,图像数据在DSP内部做好JPEG压缩后,以相同的方式通过高速缓冲模块,把数据传给FPGA的存储控制模块,做到压缩图像数据的存储。

2 系统硬件电路设计

2.1 图像采集模块

本系统图像采集模块采用的摄像头为CMOS图像传感器,型号为MT9M011。CMOS图像传感器与CCD传感器相比,虽然采集出来的图像效果弱差一点,但是CMOS的成本远远低于CCD产品,而且CMOS传感器的功耗较低。图像采集模块具体设计如图2所示。

2.2 图像显示模块

图像显示模块主要作用是将FPGA采集到的数字图像,实时地转换成模拟图像数据,并输出到带VGA接口的显示器上。图像显示接口电路包括图像编码电路和VGA接口电路,其电路如图3所示。本电路中选用的图像编码芯片为AD(Analog Devices)公司的高速视频数模转换芯片,其具体型号为ADV7123KST140。该芯片具有3组独立的十位宽RGB数字输入接口和3个相对的RGB模拟输出接口,5 V或3.3 V供电都行,速度为140 MHz,低功耗。

2.3 DSP外部存储器接口电路设计

本系统中选用TI公司的超低功耗DSP(TMS320VC5502),主要是来完成图像处理算法的实现。在对外部存储器接口设计上,该DSP采用外部存储器接口(EMIF)来进行对外部存储器的扩展,具体扩展如图3所示。

TMS320VC5502的EMIF可以访问的存储空间大小为16 MB,该系统中通过配置把空间平分为4部分,EMIF的片选信号线CE3~CE0分别对应着这4个空间的选通控制。另外EMIF的组成还包括数据线D[31:0]、地址线A[21

2]、字节使能线:BE[3:0]及各类存储器的读/写控制信号线等

3 系统软件设计

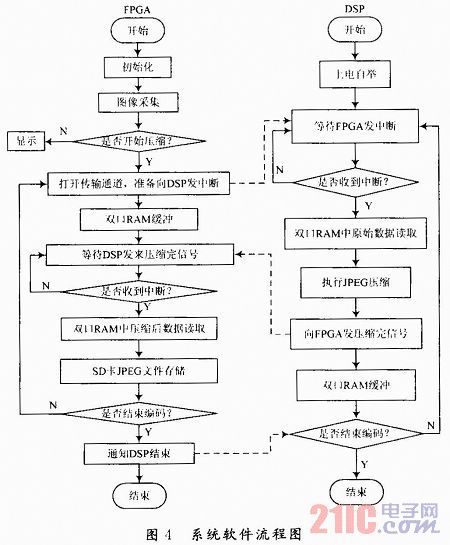

该系统的设计根据硬件结构的总体划分,也可以分为2大部分来描述。FPGA方面的软件设计主要是各功能模块的编写,如摄像头I2C配置模块、SDRAM控制器、图像图像预处理器、VGA控制器、SD卡控制器、高速缓冲器等;DSP方面的设计主要包括2方面,一方面是外部存储器驱动的编写,如SDRAM、双口RAM、FLASH等;另一方面为在DSP内部实现高效的图像压缩算法,如本文采用的JPEG压缩算法的实现。

整个系统的程序运行如图4所示,从高速压缩系统软件流程图中可以清楚的看到,FPGA和DSP各自的程序运行遵循着自己的一套规则,但是它们之间的之间又实时的完成着数据的交互。FPGA向DSP方向的指令,是通过FPGA方面设置了一个中断信号,当DSP接受到该信号的时候,就开始从双口RAM中按照规则进行原始数据的读取;DSP如果要完成向FPGA方面进行数据传输时,遵循的一个类似的执行规则,DSP会提供一个能够进行辨别的信号,让其从双口RAM中把压缩后的图像数据读进来。

4 测试结果

将FPGA上的程序下载EPCS中和将DSP开发程序烧写进FLASH(默认自举方式),对实时图像处理系统进行软硬件联合调试。设置采集和处理图像分辨率为640×480,视频YUV下采样率选4:1:1,DSP中压缩一帧图像所用的时间在23 ms左右,压缩比基本上在10:1~20:1的范围内,且SNR值基本上保证在30 dB以上。23 ms的DSP压缩时间,再加上每帧采集、传输和JPEG文件存储所用的时间,大约在31 ms左右,因此系统整体效率上能保证对采集来的图像做实时处理。测试结果表明系统的开发已经达到预定的设计要求。

5 结论

本文基于FPGA和DSP,设计了一种结构简单、成本低、性能高、功耗低的高速图像处理系统。在总结现有的FPGA与DSP高速通讯方式的基础上,提出了一种利用单片双口RAM做通信媒质完成FPGA与DSP之间数据高速通讯的结构,为实现更好的嵌入式图像处理系统提供了一个良好的解决方案。

作者:舒志猛 陈素华 来源:《现代电子技术》

免责声明:本文仅代表作者个人观点,与C114中国通信网无关。其原创性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺,请读者仅作参考,并请自行核实相关内容。

相关专题:

相关专题: