合成孔径雷达(Synthetic Aperture Radar,SAR)是一种高分辨率微波成像雷达,可以全天候、全天时地利用微波照射获得地面目标的散射信息,是获得地面信息的重要手段。它通过脉冲压缩提高距离分辨率,采用合成孔径技术提高方位向分辨率,分辨率的大小取决于信号带宽和回波多普勒带宽。提高分辨率是机载SAR的发展方向。SAR发射信号的带宽一般在几百兆,根据奈奎斯特采样定理,要求ADC的采样率最小两倍于输入信号的频率,因此高速数据采集技术越来越引起人们的关注。

1 高速数据采集系统设计方案

本系统从完成的功能方面来划分共包括数据采集和数据融合两部分;数据采集主要完成将经接收通道接收、放大、滤波并正交解调后的雷达回波信息进行模数变换和存贮;数据融合主要完成多路数据采集后数据的融合,并为接收回波信号的数字传输提供合适的接口,并将数据以要求的数据率和格式传输给后续信号处理系统。本采集系统为标准的6U插件,电路主要组成包括模拟信号调理电路、高速ADC、高速时钟管理电路、大容量数据缓存、系统时序控制电路、CPCI接口电路等,可实现四通道500 MSPS的高速数据采集,实现框图如图1所示。

1.1 核心器件ADC的选择

奈奎斯特采样定理指出:当采样频率Ωs>2Ωm(Ωm为输入信号的最高频率)时,采样后的信号可惟一地恢复原模拟信号。给定一个连续时间信号xc(t),采样后的离散时间信号xs可表示为原信号与一个周期脉冲串p(t)的乘积,如式(1)所示,其中T为采样周期。

式中:Ωs=2 π/T,为采样频率。设xc(t)为一个带限信号,带宽为ΩN,当|Ω|>ΩN时,Xc(jΩ)=0,由式(2)可见,xc(t)经采样后的频谱Xs(jΩ)就是将Xc(jΩ)在频率轴上搬移到0,±Ωs,±2Ωs,…,±nΩs处。因此,唯有当Ωs>2ΩN时,频谱不会发生混叠。

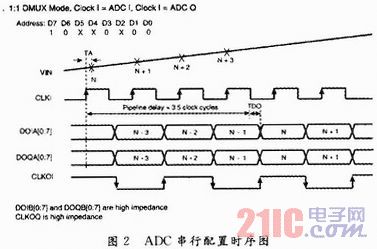

雷达系统要求中频输入信号为0~200 MHz,根据上述分析,ADC的采样时钟必须大于400 MHz,因此本电路选用一款低功耗双通道高速ADC芯片,每个通道最高采样率为500 MSPS,在交错模式下双路并行采样可实现最高1 GSPS的采样,具有8 b转换精度,此芯片内部集成了1:1和1:2的数据多路分配器,并提供了LVDS电平的低电压差分信号输出,可以降低数据输出率,并且ADC输出数据可以和多种FPGA直接互联,从而节省硬件资源。此款ADC芯片的所有参数设置均可通过三线串行方式实现,在设计中,利用FPGA编程实现串行配置的工作时序,从而控制ADC的工作模式。串行配置时序图如图2所示。

1.2 其他核心器件的选择

FPGA选用Altera公司StratixⅡ系列芯片,此器件支持多种电压接口,通过软件对管脚电平设置可以与多种逻辑电平直接接口,36 384个ALMs,192个18 b×18 b的乘法器,408个M4K RAM,488个M512RAM,由于系统需要四片片外RAM进行数据缓存,采用两片FPGA可满足逻辑控制要求和数据缓存要求。

在高速数据采集系统中,时钟电路是整个系统的最关键部件。采样时钟的抖动和相位噪声会完整地传递给采样输出,从而影响系统的信噪比。本系统的采样时钟由外部时钟源提供,为ECL电平,因此只需要对输入时钟源进行电平转换及电路匹配设计,以达到ADC的时钟输入要求,选用Semiconductor公司的MC100系列芯片对时钟电路进行管理,此系列芯片传输延时220 ps,周期间抖动0.2 ps,可满足时钟分配及传输要求。

1.3 高速数字信号处理与多通道数据同步

系统所选ADC输出为LVDS电平模式,LVDS是低电压的差分信号,功耗低,噪声小,可以有效地降低对ADC模拟通道的数字干扰;每个通道的数据输出可采取1:1或1:2的降速输出,由于所选FPGA的LVDS信号输入范围是300~1 250 Mb/s,所以采用1:1的数据输出格式,在FGPA中编程对ADC进行三线串行配置来实现。FPGA自带IP核(ALTLVDS)可实现接收ADC的LVDS数据降速转换,数据的缓存及传输等逻辑控制功能均在FPGA中运用Verilog硬件语言来完成。

对于多通道高速数据采集,通道之间数据同步传输是保证后续信号处理正确实现的前提。本系统通过对采样时刻的同步和输出时序的同步设计来实现。采样时刻的同步即保证每个通道采样时钟的一致,在电路设计时,采用单路时钟输入,然后通过同步时钟管理电路将采样时钟分配给每一个通道,并保证路径等长;时序一致性包括:一方面,每个通道ADC的三线串行配置通过严格的同步时序来控制;另一方面,每个通道都以同一个脉冲触发信号的上升沿或下降沿为起始标志进行数据缓存和传输。此触发信号和工作时钟完全同步,作为整个系统的同步信号。这样就保证了各个通道之间数据传输的同步。

1.4 性能测试

由信号源产生系统时钟和输入信号,对高速数据采集系统进行性能测试,测试结果如图3所示。其中,图3(a)是本采集系统实物图;图3(b)为线性调频信号经高速采样后恢复的时域波形图;图3(c)为80 MHz单点频信号采样频谱图,并给出了信噪比、无杂散动态范围等指标测试值;图3(d)为200 MHz带宽内各点频信号测试信噪比(SNR)。从测试结果可以看出,本系统SNR大于40 dB,信号频率相对纯净,满足雷达系统的指标要求。

2 高速PCB设计

2.1 电源地设计

电源地设计是高速PCB设计中最关键的技术。本系统存在着多种工作电压,在设计时需将模拟和数字电路独立供电,且数字电源与模拟电源之间加铁氧体磁珠隔离,构成无源滤波电路。并且同一电压的不同电源品种采用星形连接进行隔离。另外,在电源输入端放置一个100μF钽电解电容,用来消除低频噪声,而在电路板每个集成电路的电源和地之间放置一个0.1μF的高频贴片电容用于滤除高频噪声。由于电路中电压品种较多,需要对电源层进行合理分割,使不同的分割块与不同的电路单元相对应。

在高速电路中,需要设计大面积的接地层,因为接地层不仅为高频电流提供了一个低阻的返回回路,而且由于接地层的屏蔽效应,减少了外界的电磁干扰对电路的影响。不同品种模拟地和数字地之间也通过铁氧体磁珠进行隔离,为星形连接,最终通过一点连接在一起。值得注意的一点是,要使得信号通过尽可能短地回路从而减小电磁辐射。

2.2 阻抗匹配

终端匹配和阻抗控制是最简单且有效的高速PCB设计技术。合理的使用终端匹配可以有效降低信号反射和振荡。本电路设计中采取驱动端串行电阻,接收端使用差分电阻端接,并且对信号传输线进行阻抗控制。使高速信号传输路径的阻抗尽量保持连续,从而减小信号畸变和反射。

2.3 抗干扰设计

串扰问题是高速电路设计中需要重点考虑的问题。简单的减小串扰的方法可以通过增大信号走线的线间距来达到。另外,有一些特殊要求的信号线,如高速时钟线,需要进行屏蔽设计,具体做法就是在其两边并行走两条地线,这两条地线需良好接地,时钟芯片下面不要布线,否则将可能产生高频干扰,从而使时钟芯片输出产生抖动。高速ADC的输出数据线之间要求尽量等长,高速SRAM的数据总线采用等长设计,从而抑制PCB印制导线的串扰和辐射。

3 结论

本文详细介绍了四通道高速数据采集系统的设计方案,以FPGA为核心,通过Verilog语言对ADC进行模式控制,采用FPGA内部RAM与片外SRAM相结合的方式进行数据缓存,给出了实验结果,并且阐述了本电路高速PCB设计要点。本系统已成功应用于某SAR中,并完成检飞实验。

作者:张奕 余海龙 谭剑美 来源:现代电子技术

相关专题:

相关专题: